Samsung First To 3nm

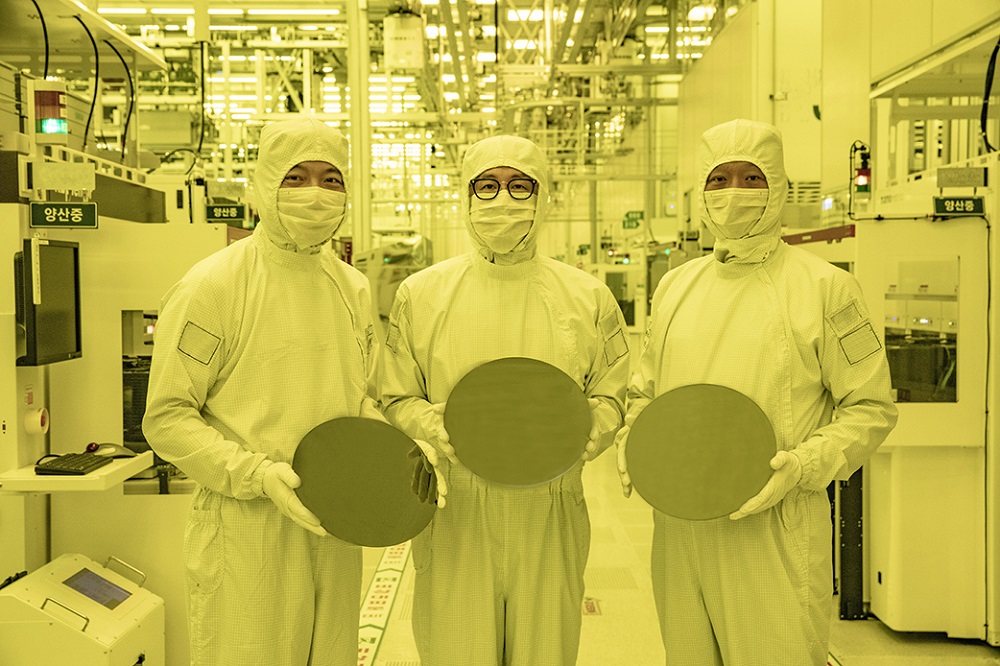

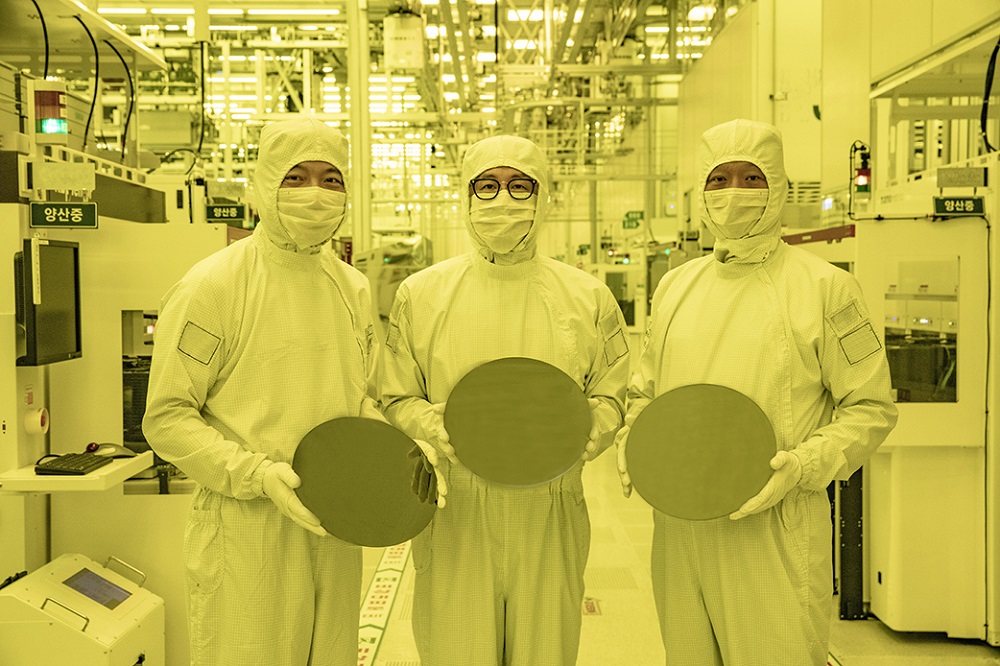

Today, Samsung announced that it has started initial production of its 3nm process node applying Gate-All-Around (GAA) transistor architecture.

“Multi-Bridge-Channel FET (MBCFET), Samsung’s GAA technology defies the performance limitations of FinFET, improving power efficiency by reducing the supply voltage level, while also enhancing performance by increasing drive current capability,” says a statement from Samsung.

Samsung is starting the first application of the nanosheet transistor with ICs for HPC applications and plans to expand to mobile processors.

Samsung’s technology utilises nanosheets with wider channels, which allow higher performance and greater energy efficiency compared to GAA technologies using nanowires with narrower channels.

Utilising the 3nm GAA technology, Samsung will be able to adjust the channel width of the nanosheet in order to optimize power usage and performance to meet various customer needs.

The design flexibility of GAA is advantageous for Design Technology Co-Optimization (DTCO), which helps boost Power, Performance, Area (PPA) benefits.

Compared to the 5nm process, the first-generation 3nm process can reduce power consumption by up to 45%, improve performance by 23% and reduce area by 16% compared to 5nm, while the second-generation 3nm process is to reduce power consumption by up to 50%, improve performance by 30% and reduce area by 35%.